採用了分層和電路塊的模塊設計

Design Gateway可以將希望標準化的功能塊或模塊作爲標準電路塊進行庫化,標準電路塊在沿用該模塊的電路中可以像元器件庫那樣進行搜索和輸入。

另外,電路塊在沿用目的地中可設定各種編輯權限,沿用設計時可使用與應用相對應的電路塊。

沿用源電路塊更新時,可以按元器件、NET等對象提取與沿用目的地電路塊的差異。

另外,在沿用目的地電路塊中反映沿用源電路塊的信息時,由於能够按差異保持沿用目的地的信息,因此也能應對希望使沿用目的地電路塊的編輯內容優先的情况。

Design Gateway是支持包括單個PCB板、或多個PCB板與PCB板之間的連接在內的整個系統電路的設計/驗證的電路設計環境,在世界上尚無先例。能够以多個PCB板爲對象進行分析和設計變更,開放性高,可與IT通信基礎設施密切協作。

另外,支持對自上向下/自下向上設計進行輔助的分層功能、使用了標準電路塊的沿用設計、以及在電氣模塊化設計中的運用等,預期可大幅削减工時,提高質量。

Design Gateway可以將希望標準化的功能塊或模塊作爲標準電路塊進行庫化,標準電路塊在沿用該模塊的電路中可以像元器件庫那樣進行搜索和輸入。

另外,電路塊在沿用目的地中可設定各種編輯權限,沿用設計時可使用與應用相對應的電路塊。

沿用源電路塊更新時,可以按元器件、NET等對象提取與沿用目的地電路塊的差異。

另外,在沿用目的地電路塊中反映沿用源電路塊的信息時,由於能够按差異保持沿用目的地的信息,因此也能應對希望使沿用目的地電路塊的編輯內容優先的情况。

Design Gateway可以根據元器件或NET中設定的屬性,進行各種規則校驗。由於不使用仿真器,因此只需最低限度的必要信息即可進行實用性很高的校驗。

通過在NET中設定電壓值,可以實施納入了元器件的電氣特性(常數、額定值)的元器件可靠性校驗,立即發現疏忽大意導致的設計錯誤,比如元器件反向連接、元器件選擇錯誤導致的額定值不足等。

除了考慮了電氣特性的校驗以外,還可以進行參照的重複、NET名稱的重複和接觸、電源/地線的短路以及屬性的遺漏等校驗,並以錯誤報告書的形式顯示結果。錯誤報告書可以與電路圖進行交叉搜索,迅速確認錯誤部位。

Design Gateway可以在電路設計初期階段輕鬆地進行SI分析。分析工具具備下列特點,任何人都能輕鬆使用。

● 模型設定簡便易行(無模型、自動分配)

● 直觀半自動化的簡便操作面板

● 以對比圖等適合分析的形式輸出結果

● 追求結果的重複使用性(重新顯示、加工、文檔化)

在設計中途也可以立即分析關鍵NET,因此消除了在電路完成之後將所有NET都輸出到仿真系統之類的繁瑣性。

Design Gateway支持Windows的標準API“COM”,開放性高,可與電路設計時需要的基礎設施環境中積累的技術信息無縫協作。

不但可以與Engineering PLM DS-2無縫協作,而且還可以與原有系統協同作業,構建用戶特有的設計環境。根據不同協作方式,備有合適的界面。

實現了“DS-CR Embedded for Design Gateway”,可以在Design Gateway上使用DS-CR功能直接訪問DS-CR管理的元器件信息及設計信息。由此,可以进一步强化电路設計环境。

・ 元器件主信息的使用

・ PCB板元器件列表的創建及管理

・ 設計數據的管理及使用

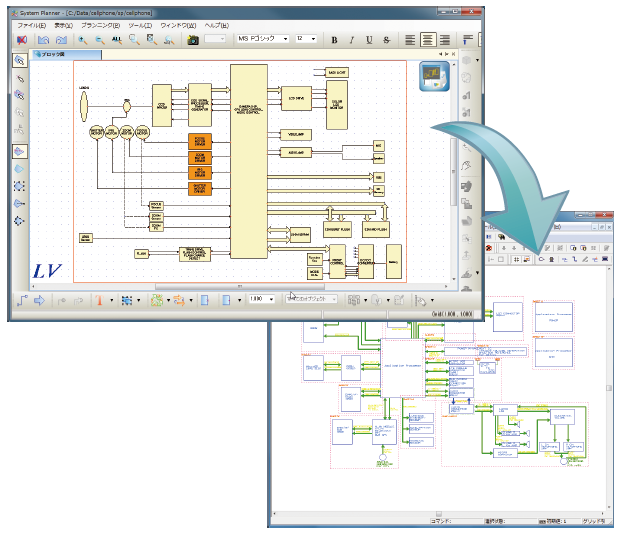

構思設計環境“System Planner”中創建的系統圖,可以直接作爲Design Gateway的系統電路讀入。

另外,可以從系統電路創建對應於多個PCB板的網表信息,利用系統級多板設計環境Design Force,在連接了多個PCB板的狀態下進行多板佈局設計。

支持使用了FPGA/CPLD、嵌入設備專用微處理器的設計,實現了與設備供應商的密切協作。

可與PCB-FPGA協同設計輔助工具“GPM”協同作業,支持設備供應商提供的FPGA開發工具、設計工具包。

另外,爲了支持難度日益加大的電子設備設計,通過與第三方供應商的設計工具實現密切協作,來强有力地支持整個電路設計/驗證環境。